セキュア集積回路研究チーム研究チームについて

集積回路で守る技術/集積回路を守る技術

認証システムに必要不可欠な暗号回路や半導体チップの真贋判定を行うPUFの研究開発に加え、フレキシブル印刷デバイスやAI処理エンジンの安全な利用を実現するセキュア集積回路の設計・製造手法の研究開発を推進しています。

認証システムに必要不可欠な暗号回路や半導体チップの真贋判定を行うPUFの研究開発に加え、フレキシブル印刷デバイスやAI処理エンジンの安全な利用を実現するセキュア集積回路の設計・製造手法の研究開発を推進しています。

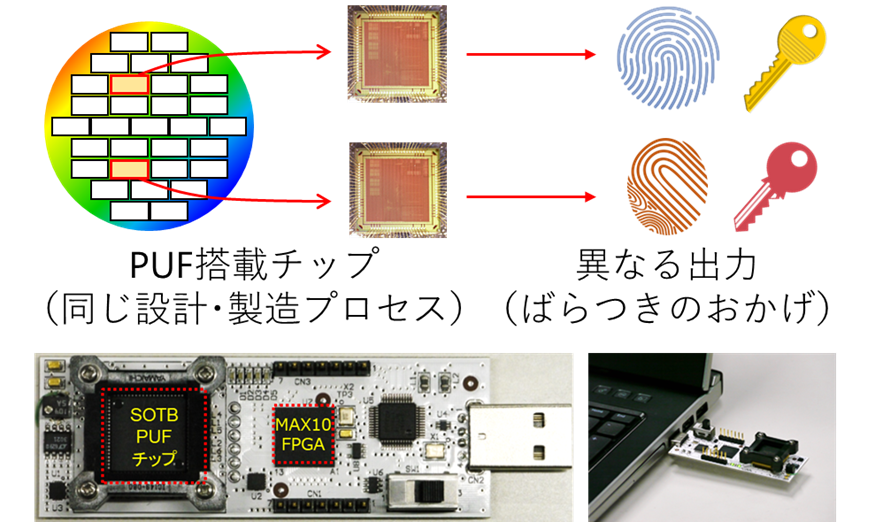

半導体チップの真贋判定や信頼基点 (Root of Trust) の構築手法の研究

印刷デバイスによるデジタル回路の実現

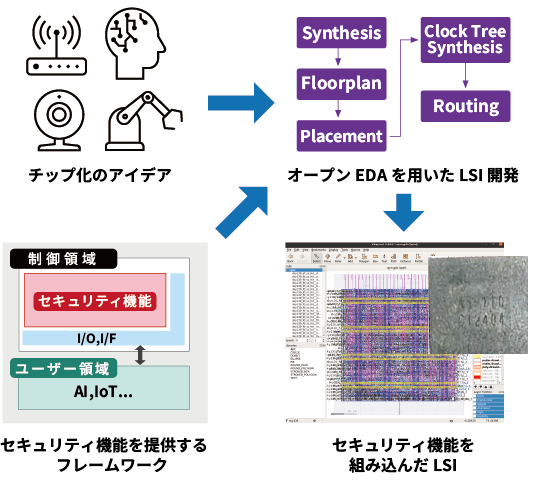

オープンソースEDAを用いたセキュア集積回路設計

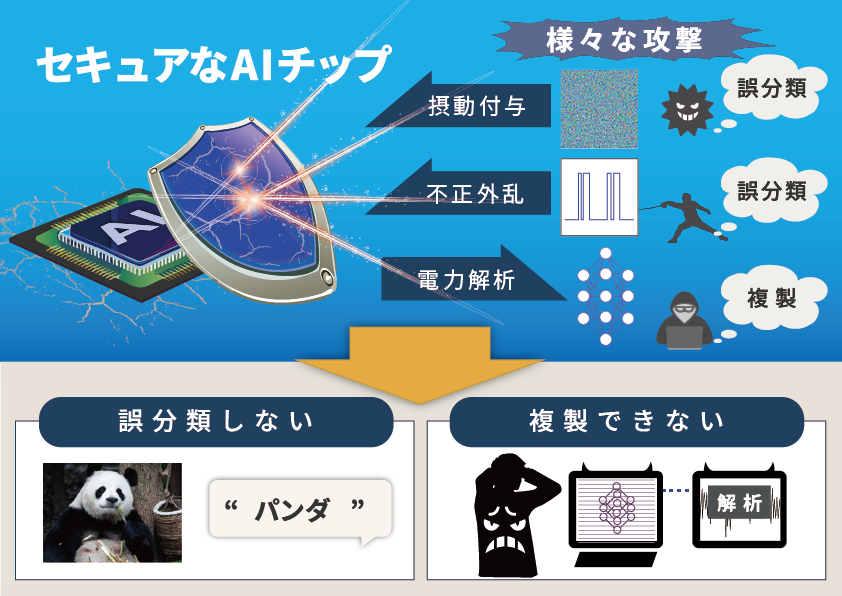

AI処理を高速化するハードウェアエンジンのセキュリティ確保

半導体は民生品から産業製品、重要インフラなどあらゆるところで使われており、快適で利便性の高い社会の実現に必要不可欠なものとなっています。一方で、半導体製品の模倣品やIoTデバイスからの情報漏えいは年々増加しています。安心・安全なIoT/CPSのためには、半導体製品が「ホンモノ」であり、扱うデータのセキュリティが担保される必要があります。そこで我々は、半導体の「ばらつき」を利用して個々のICチップを認証したり、暗号鍵を生成してデータを保護したりするPUF (Physically Unclonable Function) の研究開発等を行っています。

フレキシブル印刷デバイスは、安価かつ広い面積への回路形成が可能であり、自由に折り曲げられる薄型・軽量な回路の実現を目指す技術です。近年、AI技術が実世界で幅広く応用される中、AIと実世界を繋ぐインタフェースとして、センサデバイスの重要性が一層高まっています。本研究では、フレキシブルなフィルム上に印刷技術を用いることで、センサ機能だけでなく、データ通信、セキュリティ機能、動作スケジュール管理といった高度な機能を備えた一体型センサデバイスを実現することを目的としています。これにより、様々な環境や用途で活用可能な柔軟で安全なIoTデバイスの普及、発展に貢献します。

近年、オープンソースのEDAツールを用いた半導体回路の設計が盛んに行われており、半導体チップを容易かつ安価に作製することができるようになってきました。一方で、誰でも半導体チップを作製できるようになると、悪意のある者が不正回路を埋め込んだチップを流通させてしまう可能性もあります。そこで我々は、不正回路を混入させないセキュアな設計手法の研究開発を行っています。

深層学習に代表される人工知能 (AI) の性能が飛躍的に向上するとともに、AIが扱うデータ量も爆発的に増大しています。それに伴い、AIが消費するエネルギーも増加の一途をたどっています。AIの処理能力を向上させつつ消費エネルギーを抑えるためには、AI専用チップの開発が必要不可欠です。このようなAIチップには、画像・文書の生成や画像認識等を行うためのAIモデルが実装されています。AIモデルは各社のノウハウがつぎ込まれた重要なデータです。このチップ上のAIモデルを盗み出す攻撃や、AIチップの推論を誤らせる攻撃が報告されています。我々は、AIチップのセキュリティ確保に向けた研究開発に取り組んでいます。