CMOSインテグレーション研究チーム研究チームについて

ナノメートルの技術

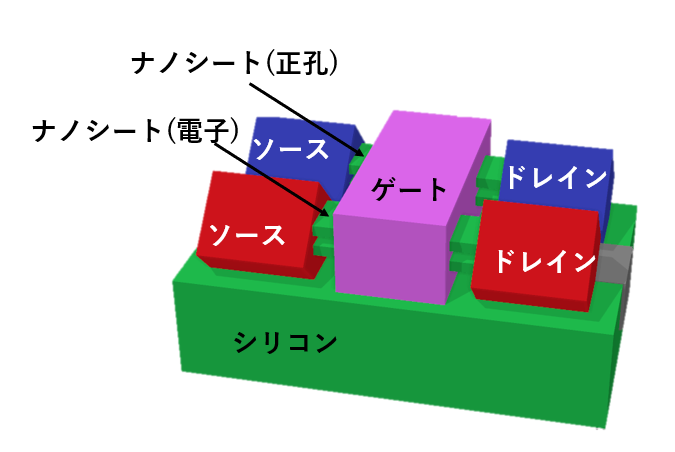

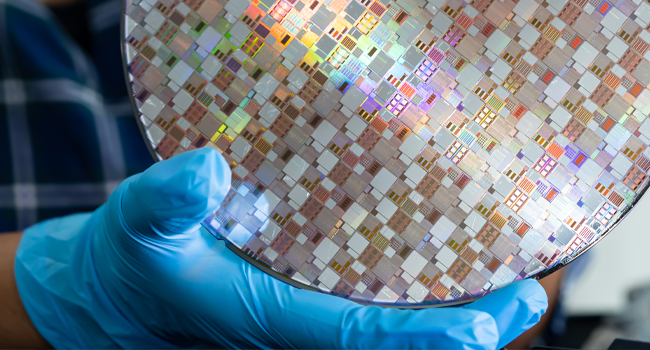

半導体集積回路はn型トランジスタとp型トランジスタを連結した相補型電界効果型トランジスタ(CMOS)と呼ばれる素子を多数集積化して構成されています。CMOS素子は年を追うごとに微細化し、現在の最先端集積回路では10億個を超えるトランジスタが集積されています。またトランジスタ構造も平面型からゲートオールアラウンド型構造に劇的に進化しています。

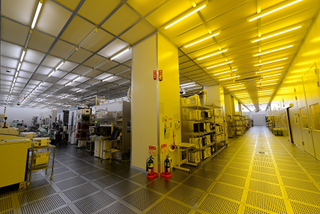

このような劇的な半導体CMOSの進化の中、私たちは数技術世代に亘って適用可能な半導体の製造プロセス技術を産総研つくば西事業所のスーパークリーンルームを舞台として開発しております。