集積回路設計研究チーム研究チームについて

半導体で世界を変える

AI処理を高効率・低電力で実行する回路技術、量子コンピュータ向けクライオCMOS回路技術、物理センサや化学センサ向けアナログ・デジタル集積回路技術の研究開発並びに、オープンソースEDAを活用したLSI設計開発環境の開拓を推進しています。

AI処理を高効率・低電力で実行する回路技術、量子コンピュータ向けクライオCMOS回路技術、物理センサや化学センサ向けアナログ・デジタル集積回路技術の研究開発並びに、オープンソースEDAを活用したLSI設計開発環境の開拓を推進しています。

センサ向けにカスタマイズされたアナデジ混載半導体チップ設計技術の創出

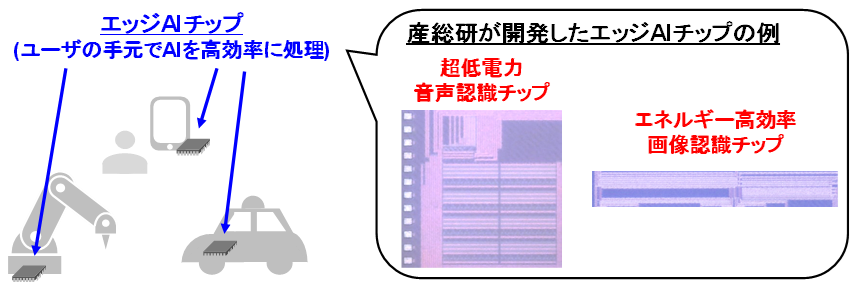

超高効率にAI処理を実行可能なエッジAIチップの研究開発

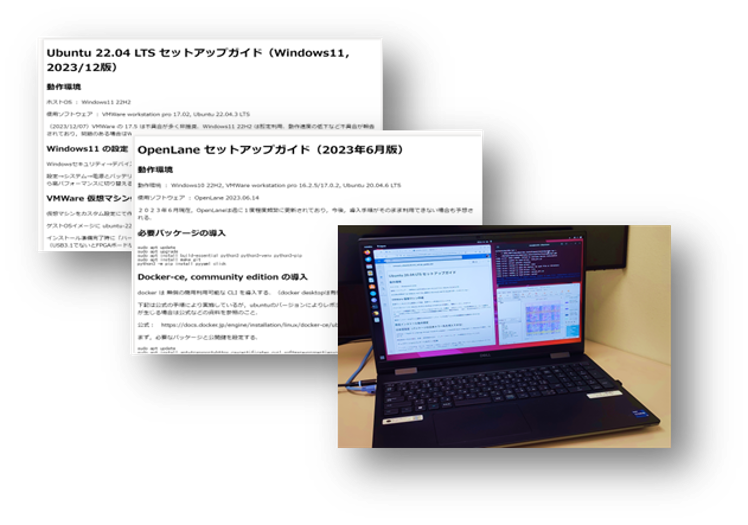

オープンソースEDAを活用したLSI開発環境の開拓

MEMSセンサ向けのアナログ・デジタル回路には、低ノイズ増幅器やAD変換器、デジタル回路など様々な要素技術が含まれます。本研究では、まずセンサデバイスの等価回路モデル化を行い、次に適切な回路アーキテクチャを創出します。また、デジタル回路による自動補正技術などを駆使して、目標仕様・コストを達成する独自の設計アプローチを提案しています。また、センサに限らずアクチュエータやエナジーハーベスティング等に向けた回路についても、同様の手法でセンサ・回路の全体最適化を図ることが可能です。

深層学習に代表されるAIは、その膨大な計算量からデータセンターで処理される事が現在は大半ですが、ユーザとデータセンターの間の通信に必要な電力や遅延時間、セキュリティの懸念から、ユーザの手元(エッジ)でAI処理を実行する事が望まれています。一方で、ユーザの手元にあるスマートフォンなどのデバイスは、使用できる電力に制限がある場合も多く、AIを高効率に処理する専用回路、所謂エッジAIチップが必要です。そこで我々は、超高効率にAI処理を実行可能なエッジAIチップの研究開発を行っています。

オープンソースEDAは世界的な潮流となっており、国内の利用事例も徐々に増え始めています。本研究では国内のオープンソースEDA/PDKの利用普及に向けた利用環境の開拓や利用に係る知見を蓄積しています。