デバイスプロセス研究チーム研究チームについて

半導体デバイスの更なる進化へ向けた挑戦

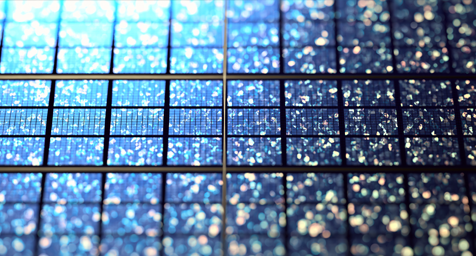

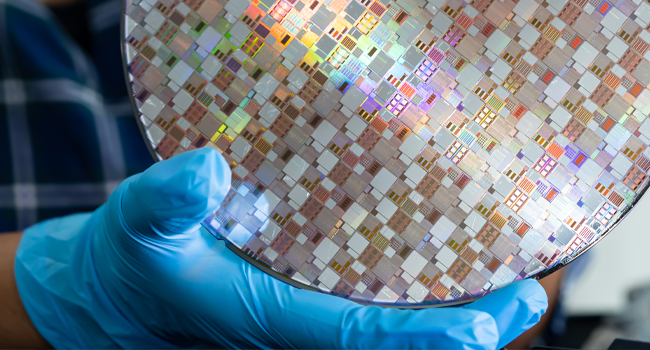

2 nmノード以降の半導体集積回路で用いられるナノシート型トランジスタ等の最先端デバイス開発に取り組んでいます。デバイス高性能・低消費電力化や高信頼性化のための、要素プロセス・材料開発を最先端300 mm装置を駆使して実施し、デバイス実証へ繋げるべく研究を進めています。また、他チームと連携し、Siデバイスの限界突破を見据えた、新材料デバイスの研究にも取り組んでいます。