3D Integration Technology Research TeamAbout

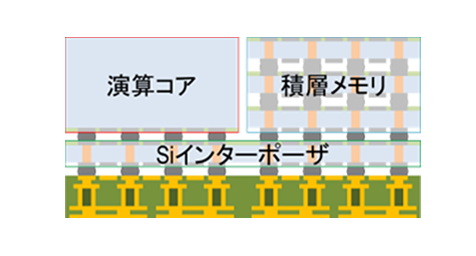

Higher performance by 3DIC technology.

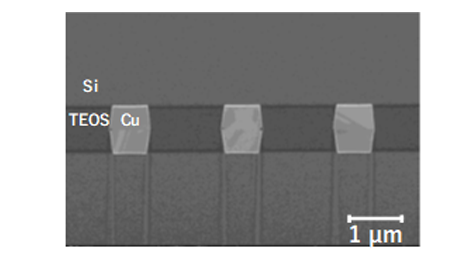

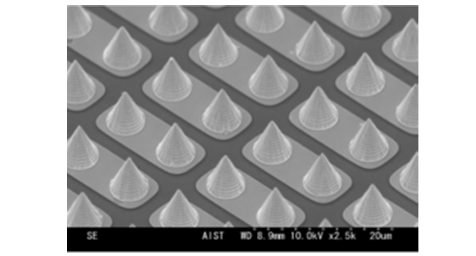

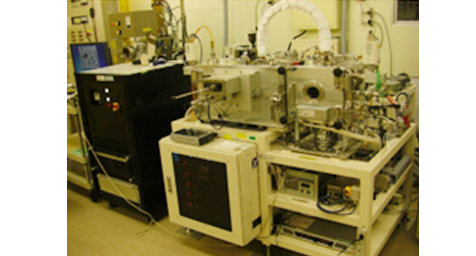

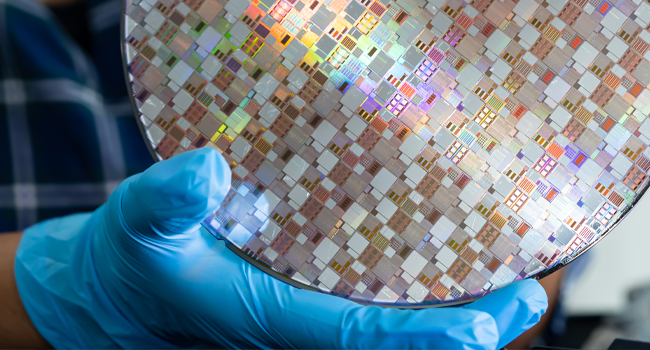

We are conducting research and development on building an integrated circuit design platform with a chiplet structure and increasing the scale of superconducting quantum computing systems by applying 3DIC technology. Manufacturing of through-Si via (TSV), narrow pitch bump formation, and direct bonding are also developed as our core technology. In addition to these fabrication techniques, we are also researching electrical and thermal analysis and electrical, evaluation and reliability.