パワーデバイス研究チーム

ワイドギャップ半導体パワーデバイスの普及拡大を目指し、 高性能・高信頼のパワーデバイスを開発しています。特にSiCおよびGaNを基板材料とした 新規デバイスを世界に先駆けて性能実証すること、及びブレークスルーをもたらす基盤技術の創出を目指し研究を行ってます。

チームの研究課題または研究成果など

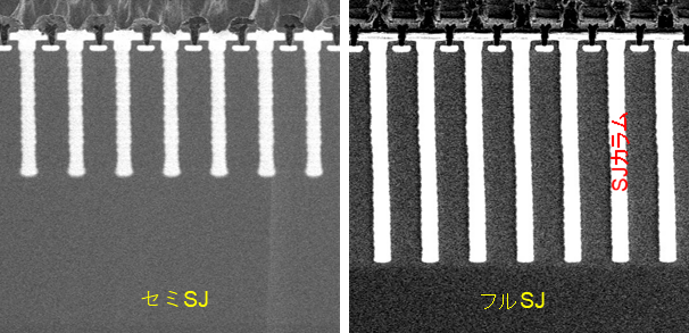

SiCパワーデバイスの研究

SiCパワーデバイスの本格実用化に向け、低オン抵抗化、高信頼化を重点課題として取り組んでいます。これまで、プレーナーゲートとトレンチゲートMOSFETの社会実装に成功し、更にショットキー内蔵型MOSFETの独自構造であるSWITCH-MOSなど新規デバイスを開発してきました。近年では更なる低オン抵抗化を目指し、世界に先駆けてスーパージャンクションMOSFETの開発を行っています。

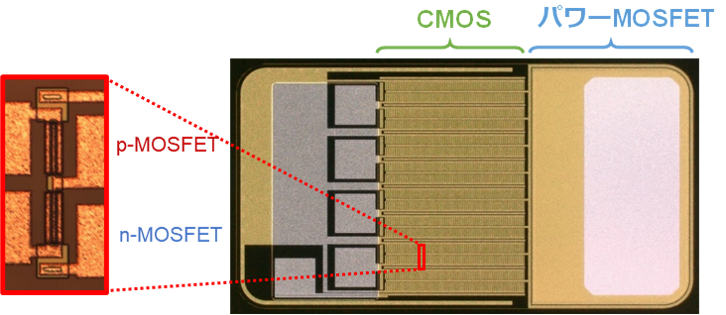

SiCパワーICの研究

SiCパワーデバイスの更なる損失低減には、高速スイッチングによるスイッチング損失の低減が必要です。パワーデバイスを駆動するゲートドライバを一体化できれば高速制御が可能になると考え、SiCのCMOS駆動回路と縦型パワーデバイスを同一チップに集積したSiCモノリシックパワーICを開発しています。

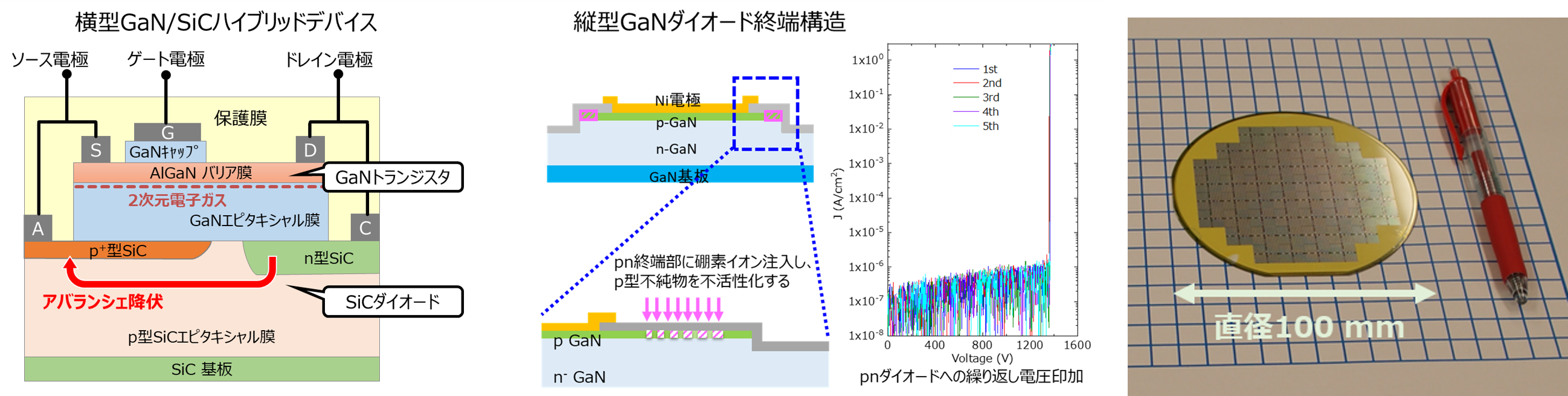

GaNパワーデバイスの研究

GaN半導体は高い伝導特性、高速なスイッチング特性が期待されていますが、パワーデバイスに必須のpn終端構造が実現していないことで、電圧印可に対して脆弱で、車載用など高い信頼性が要求される応用への展開が進んでいません。SiCデバイス開発で培った技術を活用するなど、強みを生かした独自のアプローチで課題を解決し、高信頼GaNパワーデバイスの実用化、および適用範囲拡大を目指しています。

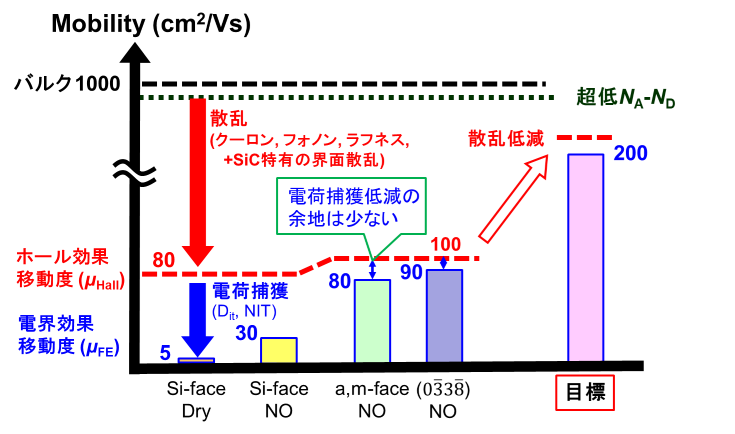

MOS界面制御の研究

SiCおよびGaNのパワーMOSFET作製におけるキープロセスはMOSゲート酸化膜形成です。これまでSiC-MOSFETのチャネル移動度の律速要因としてMOS界面トラップとチャネル電子密度の関係を明らかにしてきました。今後は移動する電子の散乱機構も明らかにし、散乱を抑制するゲート酸化膜形成プロセスを開発します。得られた知見はGaNなど次世代材料へ展開していく予定です。

主要特許・論文

- M. Okada, S. Kyogoku, T. Kumazawa, J. Saito, T. Morimoto, M. Takei, and S. Harada, “Superior Short-Circuit Performance of SiC Superjunction MOSFET” International Symposium on Power Semiconductor Devices & ICs (ISPSD), pp. 70–73, (2020).

- H. Hirai, T. Hatakeyama, M. Sometani, M. Okamoto, S. Harada, H. Okumura, H. Yamaguchi, “Difference in electron mobility at 4H–SiC/SiO2 interfaces with various crystal faces originating from effective-field-dependent scattering”, Applied Physics Letters 117, 042101 (2020).

- M. Baba, T. Tawara, T. Morimoto, and S. Harada, M. Takei, and H. Kimura, “Ultra-Low Specific on-Resistance Achieved in 3.3 kV-Class SiC Superjunction MOSFET” International Symposium on Power Semiconductor Devices & ICs (ISPSD), pp. 83–86, (2021).

- M. Okamoto, A. Yao, H. Sato, and S. Harada, “First Demonstration of a Monolithic SiC Power IC Integrating a Vertical MOSFET with a CMOS Gate Buffer”, International Symposium on Power Semiconductor Devices & ICs (ISPSD), pp. 71–74, (2021).

- Y. Miura, H. Hirai, A. Nakajima, and S. Harada, “A New JTE Technique for Vertical GaN Power Devices by Conductivity Control Using Boron Implantation into p-Type Layer”, International Symposium on Power Semiconductor Devices & ICs (ISPSD), pp. 343–346, (2021).

- A. Nakajima, H. Hirai, Y. Miura and S. Harada, “1.2 kV GaN/SiC-based Hybrid High Electron Mobility Transistor with Non-destructive Breakdown”, IEEE International Electron Devices Meeting (IEDM), pp. 777-780 (2021).

- H. Hirai, Y. Miura, A. Nakajima, S. Harada, H. Yamaguchi, “Crystal-orientation-dependent flatband voltage of non-polar GaN MOS interfaces investigated using trench sidewall capacitors”, Applied Physics Letters 119, 071601 (2021).

- S. Sekine, M. Okada, T. Kumazawa, M. Sometani, H. Hirai, N. Serizawa, R. Hasunuma, M. Okamoto, S. Harada, “Free carrier density enhancement of 4H-SiC Si-face MOSFET by Ba diffusion process and NO passivation”, Japanese Journal of Applied Physics 60, SBBD08 (2021).

- M. Sometani, K. Oozono, S. Ji, T. Morimoto, T. Kato, K. Kojima, and S. Harada, “Comparative Study of Performance of SiC SJ-MOSFETs Formed by Multi-epitaxial Growth and Trench-filling Epitaxial Growth” International Symposium on Power Semiconductor Devices & ICs (ISPSD), pp. 337–340, (2022).

- Y. Miura, H. Hirai, A. Nakajima, and S. Harada, “Wafer-scale Fabrication of Vertical GaN p-n Diodes with Graded JTE Structures Using Multiple-zone Boron Implantation”, International Symposium on Power Semiconductor Devices & ICs (ISPSD), pp. 329–332, (2022).

- T. Hatakeyama, H. Hirai, M. Sometani, D. Okamoto, M. Okamoto, S. Harada, “Dipole scattering at the interface: The origin of low mobility observed in SiC MOSFETs”, Journal of Applied Physics 131, 145701 (2022).

- M. Sometani, Y. Nishiya, R. Kondo, R. Inohana, H. Zeng, H. Hirai, D. Okamoto, Y. Matsushita, T. Umeda, “Energy levels of carbon dangling-bond center (PbC center) at 4H-SiC(0001)/SiO2 interface”, APL Materials 11, 111119 (2023).