非連続的な技術革新となる量子コンピューティングに関する基盤技術の開発、大幅な超低消費電力化、高速化を実現する集積デバイス技術等に関する技術開発を進めています。また、それらの新デバイスの設計、性能予測のためのシミュレーション技術の開発も進めています。本チームは未踏デバイス試作共用ライン(COLOMODE)の運営をしており、上記の革新的なデバイスはCOLOMODEを利用して作製しています。

80年以上にわたり、コンピュータの能力は著しく発展してきました。そして、スマートフォンという小型のコンピュータを実現しています。これまで、その発展の原動力はトランジスタ技術でした。しかし近年では、新しいコンピューティング技術による性能向上が重要となってきています。その中の1つに、量子コンピュータがあります。量子コンピュータは、交通の最適化、材料特性の予測など、従来型コンピュータが苦手とする問題を高速に解ける次世代コンピュータとして注目されています。量子コンピュータの基本素子は量子ビット素子であり、私たちは半導体シリコンを用いた量子ビット素子を用いています。現行のコンピュータやスマートフォンに搭載されている集積回路はシリコン材料でできており、成熟した集積化技術により10億個以上の素子が集積されています。シリコンベースの量子コンピュータ素子は、この集積化技術を利用可能という利点があります。

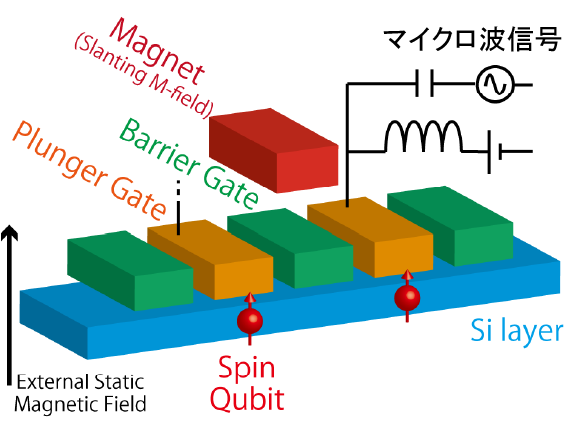

私たちが研究する量子ビットは、現行の集積回路にも使われているシリコンフィン構造を利用したスピン量子ビット素子です。一方、量子コンピュータの動作には、量子ビットの情報操作機能、情報読み出し機能、ビット間の情報を伝達するビット間結合機能など、複数の機能が必要です。私たちのチームでは、量子コンピュータハード全体を見据え、量子ビット、動作に必要な各機能、およびこれらの集積化に向けた研究をしています。

量子コンピュータは、量子ビットに閉じ込められた電子に情報を保持させ、これを操作して演算します。この情報を壊してしまう原因の一つがノイズです。このノイズ低減のために、極低温で素子特性を評価し、量子ビットに流入するノイズについても研究しています。また、大規模集積化においては、多数の素子が正しく一斉に動作する必要があります。しかし、素子加工装置の性能限界や、材料特性のばらつきにより、量子ビット特性がばらつきます。この対策に向けて、安定した微細加工が可能な試作共用ラインを利用し、素子加工に必要なプロセス技術を開発しています。さらに、素子設計のために必要となる量子デバイスシミュレータの開発と、それを活用した集積構造提案・設計も行っています。

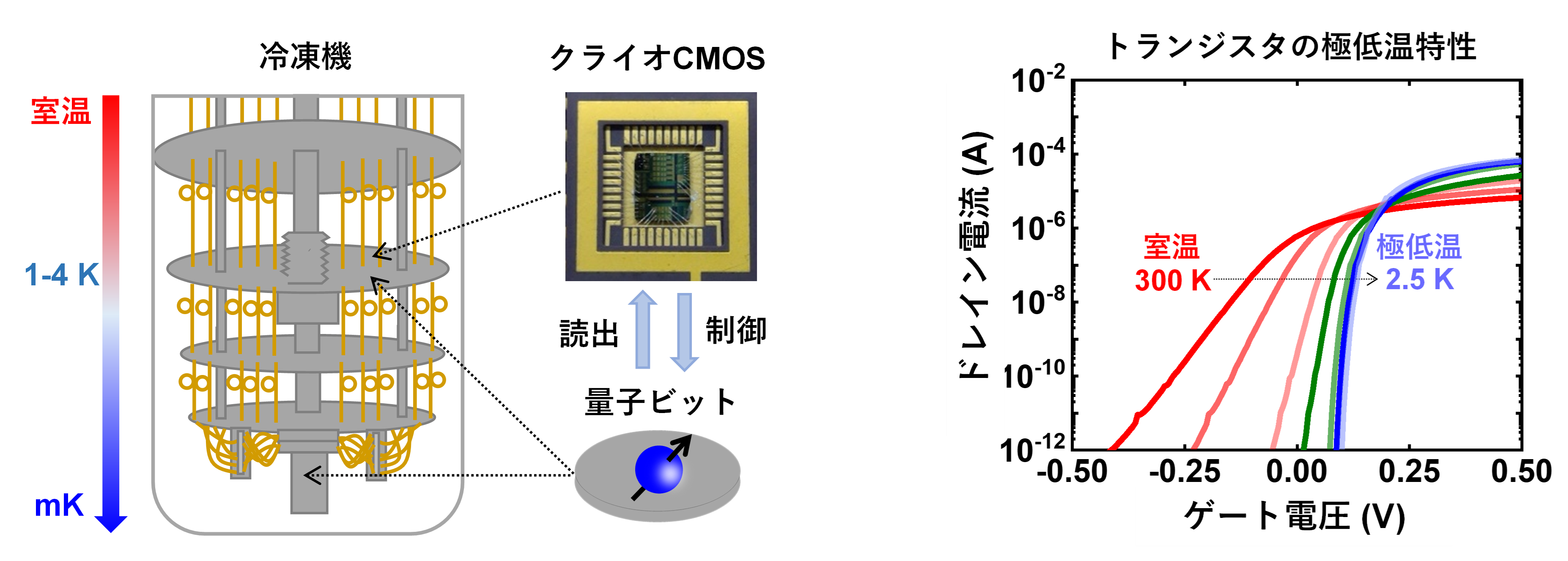

量子コンピュータには、量子ビット素子と入出力信号をやりとりする、制御・読み出し機能が必要です。これは、現代コンピュータの中央処理装置(CPU)における「演算装置」と「制御装置」の関係に相当します。超電導量子ビットやシリコン量子ビットといった固体素子型の量子ビット素子は、その量子状態を保持するために希釈冷凍機と呼ばれる大型の冷却装置の内部に格納されています。現在、その制御・読み出し機能は希釈冷凍機の外に置かれたエレクトロニクス機器群が担っており、これら機器群と量子ビットは多数の電気配線によって接続されています。このような制御形態は少数の量子ビット制御には有用ですが、集積度が向上した際には対応できません。そこで、量子ビット制御・読み出しに特化した集積回路を開発し、量子ビットと共に冷凍機内に格納することで大規模集積化に備える研究が進められています。量子ビット制御・読み出しのための集積回路は極低温下での動作が必要となるため、同技術はクライオCMOS技術と総称されています。

クライオCMOS技術による量子ビット制御・読み出しの実現には、極低温下で正確に動作する集積回路の設計や、回路を構成するトランジスタが極低温下でどのように動作するかを理解することが重要です。私たちのチームでは、極低温下で動作する電流計測回路の実証や各種デバイス物理の解明を通して、回路・デバイス技術の両面からクライオCMOS技術の研究開発を進めています。

私たちの身の回りの半導体集積回路LSIの中には、数10~100億個にも及ぶ膨大な量のMOSFETと呼ばれるスイッチが入っています。集積回路の計算処理能力の向上は、これまで、MOSFETの微細化によって達成されてきました。微細化は、高性能化と低消費電力化を同時に実現してきました。しかし、微細化による低消費電力化には限界が訪れています。そのため、低消費電力かを実現できる半導体素子の開発が、将来に向けたさらなる集積回路の性能向上に求められています。

そのような新しい半導体素子は、急峻スイッチング素子と呼ばれます。その代表候補は、トンネル電界効果トランジスタ(トンネルFET、TFET)です。TFETは量子力学的な現象であるトンネル現象を利用します。TFETの特徴は、小さな入力電圧の変化で、オフからオンへスイッチングすることができます。電圧が小さくなれば、消費電力が削減できることになります。これにより、小さな消費電力で高い計算処理能力を誇る集積回路が実現できると期待されています。

私たちのチームでは、既存製造ラインとの親和性が高く実用化に直結し得るシリコン(Si)を用いたTFET開発を行っています。TFET実用化のために最も重要な課題は、オン電流の増大です。トンネル現象が発生する確率には、様々な材料物性や量子力学的効果が関わってきます。ナノメートルオーダーの半導体素子に加工した際の材料の特徴を正しく見極め、制御しながら、実用化に繋げられるような高性能なTFETの開発に挑戦しています。