お知らせ

Qufabファウンドリの2026年度利用受付を開始しました。利用手続き詳細はこちらをご確認ください。ご興味のある方は、お気軽にお問合せください。

- Qufabは、産総研に設置された超電導デバイス作製のためのクリーンルームです。

- 2026年度はPHSTP、1KP標準施策を、それぞれ6回ずつ行う予定です。

2026年度対象

研究目的の国内外の組織、公共機関、民間企業締め切り(第一回)

申込締切 2026年3月31日(火)設計データの提出〆切 PHSTPプロセス 2026年4月27日(月)

1KPプロセス 2026年4月27日(月)

料金

お問い合わせください。仕様

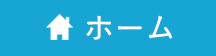

| PHSTPプロセス |

Nb層数:4 Nb/Al-AlOx/Nb ジョセフソン接合層 Mo 抵抗層 平坦化されたSiO2 層間絶縁膜 最小線幅:1.0 µm 最小ジョセフソン接合:1.0 µm角 ジョセフソン接合の臨界電流密度(Jc):10 kA/cm2 シート抵抗:2.4 Ω チップサイズ:7.1 x 7.1 mm  S. Nagasawa et al., IEICE Trans. Electron., vol. E104-C, no.9, pp. 435–445, Sep. 2021. |

|---|---|

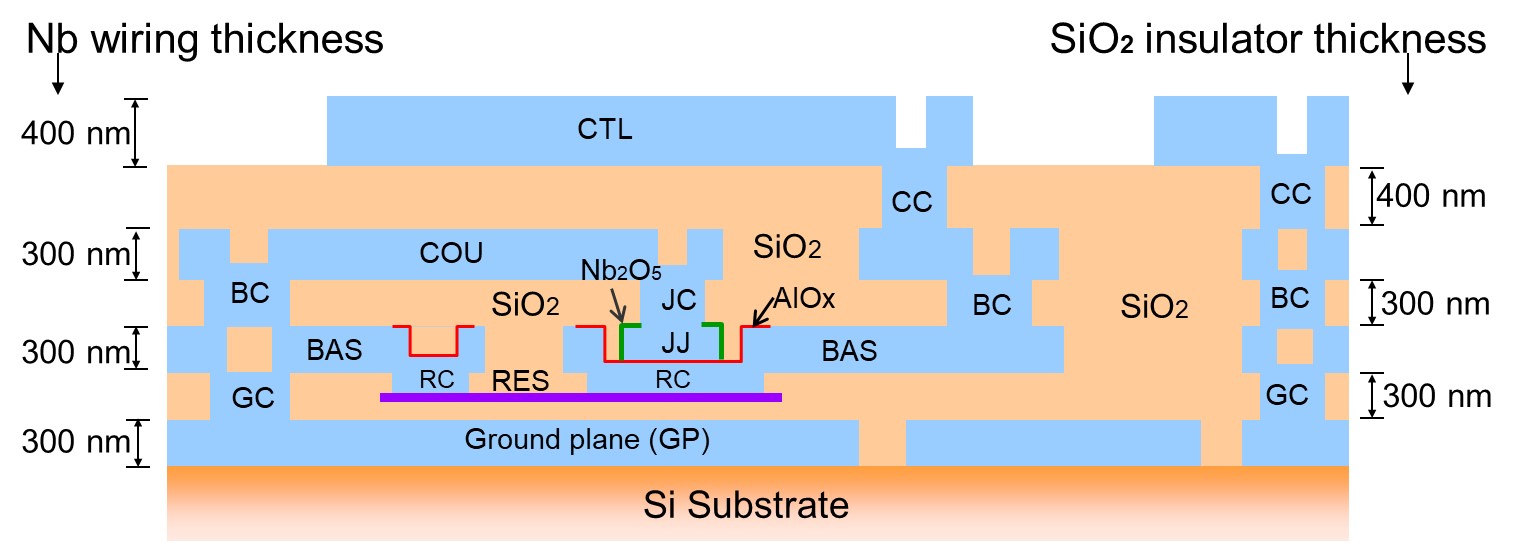

| 1KPプロセス |

Nb層数:4 Nb/Al-AlOx/Nb ジョセフソン接合層 Pd 抵抗層 平坦化されたSiO2 層間絶縁膜 最小線幅:1.0 µm 最小ジョセフソン接合:1.0 µm角 ジョセフソン接合の臨界電流密度(Jc):1 kA/cm2 シート抵抗:1.2 Ω チップサイズ:5.0 x 5.0 mm  T. Yamae et al., Sci. Rep., vol. 15, 41429, 2025. |